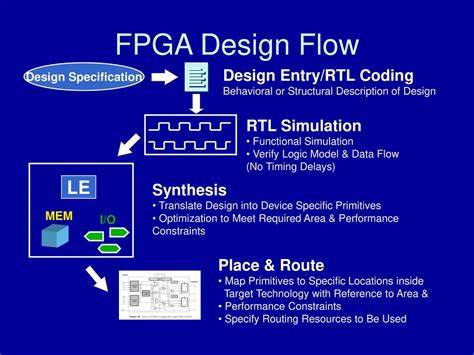

Полупроводниковые технологии стремительно развиваются, и FPGA (полевые программируемые вентильные матрицы) занимают особое место среди аппаратных решений для реализации высокопроизводительных вычислительных задач. Они используются в самых разных областях — от телекоммуникаций и обработки сигналов до искусственного интеллекта и автомобильной промышленности. Разработка FPGA стала сложной и многогранной задачей, особенно с учетом современных требований к быстродействию, гибкости и энергопотреблению. Для ускорения этого процесса появились новые программные платформы и методы, объединяющие разработку на уровне программного обеспечения с аппаратным описанием на уровне регистровой логики (RTL) и использованием стандартов OpenCL. Такой комплексный подход позволяет создавать мощные интегрированные решения и сокращать время вывода продуктов на рынок.

Одной из ведущих платформ в области гибридной разработки FPGA является AMD Vitis Unified Software Platform, которая предлагает кросс-платформенные инструменты и упрощённые потоки проектирования для различных устройств — от Zynq UltraScale+ MPSoC до Versal Adaptive SoC и Kria System-on-Modules. В основе Vitis лежит концепция гетерогенного системного проектирования, которая объединяет разнообразные вычислительные ресурсы, включая процессорные ядра, программируемую логику (PL), блока искусственного интеллекта (AI Engine) и высокоуровневую синтезу (HLS). Такое сочетание обеспечивает максимальную производительность и гибкость архитектуры. При разработке FPFA системы на базе Vitis первым этапом является создание аппаратной платформы в инструменте Vivado Design Suite. Здесь проектировщик определяет конфигурацию аппаратных блоков, включая процессорную систему, тактирование, интерфейсы передачи данных и прерывания.

Ключевым моментом становится создание платформы, которая может быть расширена с помощью пользовательских IP-ядер, высокоуровневых синтезированных (HLS) модулей и модулей RTL. Для управления сложной системой и связывания различных компонентов используется концепция Extensible Platform, что облегчает адаптацию и дальнейшее масштабирование решения. Важной особенностью современного подхода к разработке является интеграция RTL-ядер с ядрами HLS — модулями, которые описываются на языке высокого уровня, например, C++, и синтезируются в эффективную аппаратную логику. Такой подход позволяет ускорить создание цифровых фильтров, алгоритмов обработки сигналов и других специализированных функций без необходимости глубоко погружаться в детали регистровой логики. Одним из примеров успешного использования этого метода является создание ядра сглаживающего фильтра низких частот, реализованного как HLS-модуль, который получает данные с аналогового входа, обработанного через SysMon (системный монитор), преобразованный в AXI Stream поток с помощью RTL-конвертера.

Это демонстрирует, как можно объединять аппаратные блоки и программное обеспечение для реализации сложного конвейера обработки данных, минимизируя задержки и повышая энергоэффективность работы. OpenCL играет ключевую роль в гетерогенной разработке FPGA, обеспечивая единый интерфейс для программирования и управления аппаратными ядрами на низком уровне. Использование OpenCL API позволяет запускать вычислительные задачи на программируемой логике FPGA, а хост-программы — обычно запускающиеся на ARM ядрах — управляют обменом данными и контролируют выполнение. Такой подход уменьшает порог вхождения для разработчиков, знакомых с параллельным программированием на OpenCL, и ускоряет интеграцию аппаратных ускорителей в существующие системы. Важно отметить, что разработка FPGA в современном тракте связана с построением полной встроенной системы, включающей аппаратную логику, драйверы, операционную систему и прикладное ПО.

Vitis Unified Platform облегчает эту задачу, предоставляя возможность создания SD-карт с готовыми образами Linux, включая ядро, файловую систему (RootFS) и необходимые библиотеки (SysRoot). Это позволяет сразу же проводить тестирование аппаратных и программных компонентов в реальном окружении. При проектировании потоков данных между аппаратурой часто используется AXI Stream интерфейс, оптимизированный для пассивной передачи данных в режиме высокой пропускной способности и низких задержек. Конфигурация таких связей выполняется в специальном конфигурационном файле внутри проекта, упрощая согласование взаимодействия разных ядер и модулей на уровне архитектуры. Рассмотрение интеграции пользовательских RTL-модулей иллюстрирует гибкость платформы.

Например, простой конвертер данных с системного монитора в AXI Stream позволяет использовать внешние сигналы с аналоговых входов в цифровой обработке. Благодаря этому можно использовать FPGA не только для ускорения классических вычислений, но и для работы с реальными сигналами в режиме реального времени. Важным этапом является построение и компиляция всего проекта, которая включает синтез аппаратных компонентов, создание бинарного контейнера, связывание с OpenCL и генерацию образов для прошивки. Весь цикл разработки может быть проведён на Linux-машине, что способствует интеграции в современные конвейеры непрерывной интеграции и автоматизации сборок. Продвинутые возможности Vitis позволяют осуществлять аппаратное моделирование, анализ производительности, и, при необходимости, подключаться вручную к Vivado для дальнейшей оптимизации проекта.

Такой многоуровневый и многосторонний подход адаптирует процесс разработки FPGA к современным требованиям рынка, сокращая время и расходы на проектирование. С точки зрения применения, разработчики получают возможность быстро адаптировать проект под новые задачи, добавлять аппаратные ядра, связывать их с программными приложениями и использовать популярные языки программирования — от низкоуровневого RTL до высокоуровневого C++ с OpenCL. Это позволяет эффективно задействовать подготовленные аппаратные и программные ресурсы для создания специализированных вычислительных ускорителей, систем обработки данных и даже искусственного интеллекта на базе FPGA. Не менее важно и сообщество вокруг таких технологий — открытые проекты, примеры и документация позволяют новичкам получить практические знания и быстро приступить к реальной разработке. Использование платформ, подобных Vitis, значительно снижает порог вхождения в мир FPGA.

В итоге, текущие подходы в разработке FPGA сочетают мощь программируемой логики с гибкостью программного обеспечения, открывая новые горизонты в создании комплексных, производительных и адаптивных embedded-систем. Такой союз программного кода, высокоуровневой синтезы и RTL описания позволяет инженерам разрабатывать инновационные решения быстрее и эффективнее, что становится ключевым преимуществом в условиях стремительного технологического прогресса.