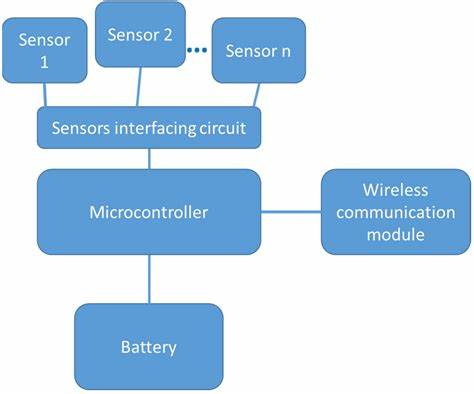

Современные технологии искусственного интеллекта стремительно внедряются во все сферы нашей жизни, от смартфонов до умных устройств в доме и промышленных решений. Одним из наиболее интересных направлений стало использование ИИ на микроконтроллерах — миниатюрных и энергоэффективных процессорах, способных работать в встраиваемых системах. Такие микроконтроллеры открывают новые возможности для решений с ограниченными ресурсами, где полноразмерные компьютеры попросту неуместны. Чтобы понять, как именно реализуется искусственный интеллект на этих устройствах, важно разобраться в том, как устроен вычислительный граф и как модель машинного обучения взаимодействует с аппаратной частью микроконтроллера.Впервые взглянув на современные микроконтроллеры, представляющие собой компактные вычислительные платформы, можно удивиться, каким сложным вычислительным процессам они способны поддать.

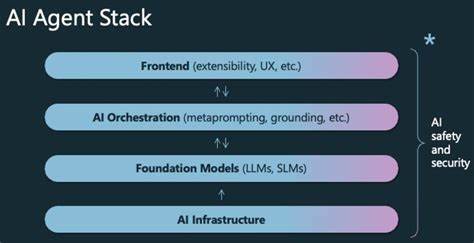

Исполнение моделей ИИ на таких ограниченных по мощности и памяти системах — задача нетривиальная. В основе этого процесса лежит вычислительный граф — структурированное последовательное описание операций, необходимых для обработки данных с целью получения результата. Этот граф состоит из узлов и связей между ними, где каждый узел представляет собой отдельный оператор или слой нейронной сети, а ребра указывают направление передачи данных.Для моделирования и инференса на микроконтроллерах часто используются компактные и оптимизированные фреймворки, одним из таких является TensorFlow Lite for Microcontrollers (tflite-micro). Он использует формат файлов .

tflite, который представляет собой бинарный контейнер, включающий в себя сам вычислительный граф, веса модели, описание операторов и их параметры. Важнейшая особенность формата заключается в том, что вся необходимая для инференса информация собрана в одном файле, что делает распространение и использование моделей максимально удобным и эффективным, особенно в условиях отсутствия полноценной файловой системы.Вычислительный граф в .tflite файле кодируется посредством FlatBuffers — высокопроизводительного бинарного формата, позволяющего эффективно хранить и манипулировать структурированными данными. Благодаря FlatBuffers можно без излишних затрат памяти и времени сразу обращаться к необходимым компонентам модели без декодирования всего файла полностью.

Это критично для микроконтроллеров с ограниченными ресурсами. Структура графа включает операторные коды (operator_codes), которые определяют, какие операции будут выполняться, и параметры операторов, обеспечивающие их корректное функционирование с конкретными входными и весовыми данными.Важной составляющей успешной работы вычислительного графа является наличие так называемого резольвера операций — компонента, который регистрирует реализации операторов, необходимые для работы конкретной модели. Поскольку модели могут содержать различные типы слоев, важна возможность гибко подключать только те ядра (kernels), которые необходимы для конкретного инференса. Например, в модели для обнаружения человека, основанной на MobileNetV1, регистрируются стандартные операторы, такие как свертка (Conv2D), пулинг (AveragePool2D), софтмакс (Softmax) и преобразования формы тензоров (Reshape).

Таким образом, с помощью резольвера можно обеспечить минимальный набор необходимого кода, повысив эффективность использования памяти.Другое популярное направление — использование пользовательских операторов, адаптированных под конкретные аппаратные возможности. Примером служит интеграция небольших нейропроцессоров, таких как Arm Ethos-U, которые способны значительно повысить производительность ИИ на специальных микроконтроллерах. В этом случае модель после компиляции через специальные инструменты объединяется в единый оператор ETHOSU — задача которого состоит в том, чтобы направлять команды и данные в аппаратное ускорение. В результате модель в .

tflite файле упрощается до минимального набора операторов, а большая часть нагрузки переносится именно на аппаратный блок, что позволяет существенно экономить вычислительные ресурсы основного микроконтроллера.Для более наглядного понимания, можно привести пример с детекцией объектов на основе модели YOLOv3-tiny, где граф строится вручную через специализированную библиотеку ggml, используемую в проектах llama.cpp и whisper.cpp. В данном случае последовательное применение сверток, пуллингов, объединений и масштабирований приводит к построению насыщенного иерархического графа — каждый оператор представляет собой отдельный этап обработки данных, на который указывают входные и выходные данные в форме тензоров.

Такое построение графа требует явного задания всех промежуточных компонентов, но взамен обеспечивает детальный контроль над процессом инференса.В противоположность этому, использование tflite-micro позволяет скрыть детали построения графа за счёт готового скомпилированного файла модели, что значительно упрощает внедрение ИИ в микроконтроллерные проекты. Процесс запуска модели сводится к инициализации резольвера операторов, загрузке модели в память, распределению ресурсов под тензоры и непосредственному вызову интерпретатора для выполнения инференса. За кулисами весь сложный вычислительный граф уже содержится в .tflite файле, а соответствующий код только задействует нужные операторы.

Интересно отметить, что при помощи инструментов вроде flatc можно декодировать .tflite файлы в удобочитаемый формат JSON, что позволяет разработчику детально проанализировать структуру вычислительного графа, определить список используемых операторов и параметры каждого узла сети. Это значительно облегчает отладку и оптимизацию моделей, особенно в условиях ограниченных ресурсов микроконтроллеров.Еще один ключевой аспект — поддержка различных форматов моделей. Например, GGUF, Safetensors или полезно известный PyTorch pickle требуют дополнительного программного обеспечения или кода, чтобы выполнить инференс, так как в них нет встроенного вычислительного графа.

В свою очередь, форматы с встраиваемым графом, как .tflite и ONNX, обладают более универсальным и переносимым форматом, что упрощает разработку кроссплатформенных решений.Технологии, позволяющие свести выполнение всего вычислительного процесса к единому оператору, демонстрируют будущее ИИ на микроконтроллерах. Благодаря ним использование нейропроцессоров и аппаратных ускорителей может происходить неявно, а модель становится эффективной и компактной. Это особенно важно для устройств с жесткими ограничениями по памяти и скорости, таких как датчики, носимые устройства и встроенные системы промышленного назначения.

В целом, вычислительный граф — это ядро всего процесса работы ИИ на микроконтроллерах. Именно он описывает последовательность операций и взаимодействие данных и весов модели, позволяя оптимизировать исполнение под конкретное железо. Разработка и кастомизация операторов, правильный выбор формата модели и инструментов компиляции — ключевые факторы успешной интеграции искусственного интеллекта в такие ограниченные системы.Понимание устройства вычислительного графа и особенностей форматов, таких как .tflite, а также механизмов регистрации и выполнения операторов помогает значительно упростить задачу внедрения ИИ.

Это знание — мост между высокоуровневым проектированием нейросетей и низкоуровневой оптимизацией для микроконтроллеров. Оно позволяет использовать возможности самых современных аппаратных платформ и открывает потенциал для создания интеллектуальных решений в самых разнообразных сферах, от медицины и промышленности до бытовых приборов и интернета вещей.Таким образом, искусственный интеллект на микроконтроллерах — это не просто сокращенная версия привычных моделей, а сложный комплекс технологий, где вычислительный граф и скомпонованный в файл формат модели играют центральную роль. Именно благодаря этим технологиям возможно добиться высокой производительности и надежности при минимальных затратах ресурсов, что открывает новые горизонты для развития встраиваемого ИИ.