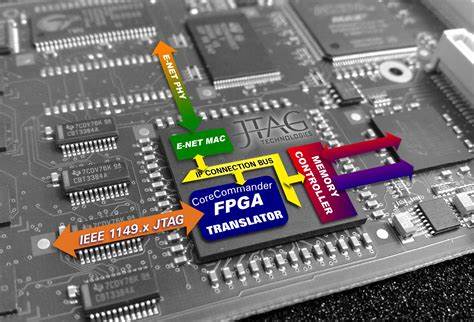

FPGA-системы все чаще используются в самых разных сферах – от промышленного контроля и автомобильной электроники до потребительской электроники и коммуникационных устройств. Несмотря на кажущуюся простоту, взаимодействие с внешними асинхронными сигналами, например, кнопками или датчиками, наносит серьезный вызов разработчикам. Кажется, что простое нажатие кнопки не может спровоцировать сбой сложного цифрового устройства, однако именно такие действия часто становятся причиной непредсказуемой работы FPGA. В этой статье мы подробно разберем причины подобных сбоев и представим действенные методы их преодоления. Понимание этих аспектов поможет не только избежать критических ошибок, но и повысить надежность конечного продукта.

Асинхронные внешние сигналы и их особенности Основная сложность работы с внешними сигналами состоит в их асинхронности относительно внутреннего тактового генератора FPGA. Цифровые схемы внутри FPGA работают на основе определенного тактового сигнала, задающего синхронизацию всех логических элементов. Внешние сигналы поступают с устройств ввода, датчиков или интерфейсов и не зависят от частоты и фазы этого тактового сигнала. Такая «отсутствие гармонии» во временных характеристиках способствует возникновению состояния, известного как метастабильность. Метастабильность – это промежуточное состояние триггера или флип-флопа, при котором выход не может приобрести однозначный логический уровень в течение определенного времени.

Это состояние возникает, когда входной сигнал меняется непосредственно вблизи фронта тактового сигнала. Вместо плавного «установки» сигнала на выходе схему может «заморозить» в неопределенном состоянии, которое может длиться нефиксированное время. Метастабильность способна распространяться на последующие логические элементы, вызывая ошибки в работе и сбои всей системы. Другой важный аспект – механический «дребезг» контактов кнопки. При физическом замыкании контактной группы переключателя происходит серия быстрых и неустойчивых переходов логического уровня, которые воспринимаются FPGA как множество отдельных нажатий.

Если данные переходы не фильтровать, система будет вести себя крайне нестабильно, например, мигать индикатором или генерировать ложные прерывания. Наконец, внешний сигнал подвержен воздействию электромагнитных помех, наводок и шумов, что также усложняет правильное считывание событий. Методы надежной синхронизации внешних сигналов Для предотвращения последствий метастабильности важно реализовать специальные схемы синхронизации. Самым распространенным решением является многоступенчатый синхронизатор – цепь из нескольких флип-флопов, включаемых последовательно, каждый из которых синхронизируется с внутренним тактовым сигналом FPGA. Принцип его работы прост: входящий асинхронный сигнал сначала попадает в первый регистр, который может перейти в метастабильное состояние, но последующие регистры снижают вероятность распространения этой метастабильности, «заглаживая» переход.

Чем больше этапов синхронизации, тем ниже вероятность ошибки. Однако на практике обычно достаточно трех ступеней, чтобы обеспечить надежность работы с MTBF (среднее время безотказной работы) вплоть до миллиардов лет. Важной частью реализации синхронизаторов является использование специальных атрибутов для флип-флопов, например, ASYNC_REG в синтезаторах Xilinx, которые оптимизируют размещение регистров и минимизируют задержки, связанные с асинхронным входом. Такой подход гарантирует, что синхронизация учитывается на уровне физического проектирования и снижает риски возникновения метастабильных состояний. Решение проблемы дребезга кнопки Механический дребезг – одна из самых распространенных проблем при работе с кнопками и переключателями.

Одного только многоступенчатого синхронизатора недостаточно, так как после стабилизации сигнала посредством регистров FPGA получает мгновенные изменения логического уровня, вызванные физическим эффектом. Для борьбы с этим применяется программный или аппаратный «дебаунсинг» – метод фильтрации быстрых колебаний сигнала. Один из самых простых и надежных способов – использование длинного сдвигового регистра внутри FPGA с системным тактовым сигналом. Сдвиговый регистр записывает состояние входного сигнала с каждым тактом – если все биты содержат единицу, значит кнопка была непрерывно нажата достаточно долго, и можно считать это истинным нажатием. Если нет, считается, что кнопка отпущена.

Такой подход легко настраивается изменением длины регистра для различных требований к периоду фильтрации. Так, например, при тактовой частоте 100 МГц сдвиговой регистр из 100 бит обеспечивает период подавления дребезга около 1 микросекунды, что с запасом покрывает типичные физические характеристики большинства механических переключателей. Благодаря простой схемотехнике и синтезируемости, данный метод широко используется в промышленной практике. Системный пример реализации и управление тактовыми сигналами Ключевым элементом любой FPGA-системы является внутренняя тактовая структура. Часто внешняя частота поступает с частотой, отличной от частоты логики.

Для обработки кнопки с надежной синхронизацией необходим внутренний клок, на который и ориентируется работа синхронизатора и схемы дебаунса. Для преобразования тактовой частоты обычно используется MMCM (Mixed-Mode Clock Manager) или PLL (Phase-Locked Loop), которые на основе входного сигнала формируют необходимую частоту с высокими характеристиками стабильности и низких джиттером. Правильная генерация тактового сигнала и контроль его состояния (например, через сигнал LOCKED) важны для корректного запуска всего синхронизирующего контура. Такой подход исключает ложные срабатывания и обеспечивает однородность временных характеристик всей системы. Тестирование и проверка корректности работы Работа с асинхронными сигналами требует тщательной проверки на всех этапах разработки.

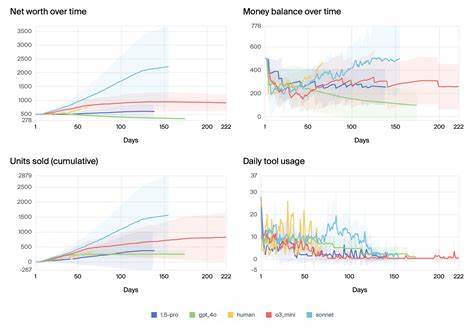

Тестбенчи и моделирование позволяют увидеть, как меняется состояние кнопки по времени, проверить отсутствие ошибок синхронизации и оценить эффективность деподживания дребезга. Качественное моделирование играет важную роль, так как некоторые метастабильности проявляются лишь в редких временных ситуациях. Анализ временных диаграмм и симуляция нажатия кнопки показывают, что внедрение многоступенчатого синхронизатора и фильтрации дребезга позволяет убрать ложные переходы и избежать сбоев системы при реальных сценариях эксплуатации. Кроме того, статический анализ CDC-инструментами (например, от Xilinx Vivado) дает возможность выявить узкие места в проекте, связанные с переходами между тактовыми доменами. Практические рекомендации и лучшие подходы Для проектирования надежной FPGA-системы с внешними сигналами стоит изначально определить критичность каждого внешнего входа и выбрать соответствующий уровень защиты от метастабильности и помех.

Не рекомендуется пропускать этап синхронизации или пытаться обходиться программными методами без аппаратной поддержки. Использование трехступенчатого синхронизатора обычно обеспечивает баланс между надежностью и ресурсами FPGA. При работе с более сложными сигналами, например, шинами данных, следует учитывать использование снете кодирования, FIFO-буферов или других подходов для безопасного переноса информации между тактовыми доменами. Дебаунсинг рекомендуется настраивать исходя из характеристик используемых кнопок и требуемых временных параметров реакции системы. Встроенный программный фильтр с помощью сдвигового регистра – оптимальное решение для большинства систем.

При больших требованиях по времени задержки можно рассмотреть альтернативные методы, такие как счетчики или FSM. Заключение Одно простое нажатие кнопки способно нарушить работу сложной FPGA-системы, если не уделить должного внимания особенностям асинхронного ввода. Метастабильность и дребезг – главные причины сбоев, но грамотное управление тактовыми доменами, многоступенчатая синхронизация и надежный фильтр дестабилизирующих сигналов позволяют создать устойчивую к ошибкам систему. Современные методы и компоненты, такие как MMCM, ASYNC_REG-атрибуты, а также проверенные схемы сдвиговых регистров, предоставляют FPGA-дизайнерам мощный набор инструментов для построения надежных интерфейсов с внешним миром. Пренебрежение этими техниками приводит к непредсказуемым багам и надежной работе системы избежать не удастся.

Необходимо проводить всестороннее тестирование, временной анализ и соблюдать правильную организацию проектных модулей. Этот фундаментальный подход к обработке внешних сигналов является залогом успешного внедрения FPGA в самых требовательных применениях – от промышленности до медицины и автомобильной электроники. Обладая знаниями о том, почему простое нажатие кнопки может вызвать сбой, и как это исправить, разработчик может спроектировать действительно надежное цифровое решение.