Современные технологии искусственного интеллекта стремительно развиваются и находят все большее применение в устройствах периферийных вычислений — от носимых гаджетов до интеллектуальных сенсоров. В этих условиях критически важными становятся энергоэффективность, надежность и прозрачность принимаемых решений. Одним из наиболее перспективных направлений, направленных на удовлетворение этих требований, является внедрение байесовских машин, которые способны выполнять байесовский вывод непосредственно на аппаратном уровне. Последние достижения в этой области связаны с созданием логарифмической мемристорной байесовской машины, которая открывает качественно новые возможности в области встроенного искусственного интеллекта и концепции вычислений на периферии. Главная идея байесовских машин заключается в аппаратной реализации байесовского вывода — основополагающего метода обработки неопределённой информации.

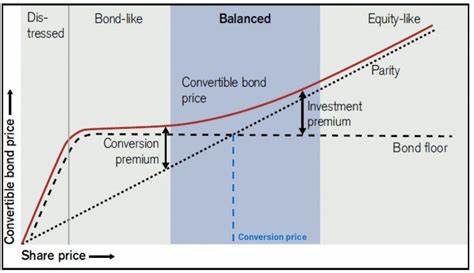

Байесовский вывод позволяет рассчитать вероятность гипотезы с учетом наблюдений и априорных данных. Такие модели особенно полезны в условиях ограниченной и шумной информации, где классические нейронные сети часто оказываются непрозрачными и требуют значительных вычислительных ресурсов. В отличие от них байесовские машины обеспечивают естественную интерпретируемость и стабильность, что критически важно для применения в медицинских или системах безопасности. Традиционные байесовские машины базировались на стохастических вычислениях, где все вероятности кодируются с помощью длинных потоков случайных битов. Умножение вероятностей реализовывалось посредством простых логических элементов, что обеспечивало высокую энергоэффективность и компактность архитектуры.

Однако в таких системах присутствуют существенные ограничения: высокая задержка из-за необходимости усреднения по множеству циклов и сложности с точной обработкой событий с очень низкой вероятностью. Последние трудности особенно проявляются в задачах, требующих работы с временными рядами и редкими событиями. В ответ на эти вызовы была разработана логарифмическая мемристорная байесовская машина, пример прототипа которой изготовлен на гибридном CMOS/мемристорном процессоре с использованием оксида гафния. Эта архитектура отказывается от стохастического кодирования в пользу логарифмического представления вероятностей в виде целочисленных данных. Благодаря этому произведение вероятностей сводится к суммированию логарифмов, что значительно упрощает арифметические операции, сокращает задержки и улучшает стабильность вычислений, особенно в областях с малыми значениями вероятностей.

Мемристоры в этой разработке играют ключевую роль как энергоэффективные многократные машины памяти, способные хранить логарифмические значения вероятностей в компактных ячейках и обеспечивать их быструю выборку с минимальными энергетическими затратами. Функция памяти совмещается с процессом вычисления, реализуя концепцию near-memory computing — вычисления вблизи источника данных, что минимизирует энергозатраты на передачу данных, типичные для классических архитектур. Одна из отличительных особенностей логарифмической байесовской машины — кодация вероятностей с помощью восьмибитных целочисленных значений, где каждая величина масштабируется по степеням базы 1/2. Такой подход не только расширяет динамический диапазон моделей, позволяя корректно учесть события с чрезвычайно низкой вероятностью, но и повышает точность вычислений в сравнении с традиционными стохастическими методами. Примером использования данной технологии служит задача классификации стадий сна на основе анализа сигналов электроэнцефалографии и электромиографии.

Эта задача демонстрирует особенности временных моделей с зависимостью состояний в последовательные моменты времени и требует корректной обработки редких переходов между фазами сна. Использование логарифмической байесовской машины позволило успешно выполнить классификацию с точностью, сопоставимой с программными моделями, но с намного меньшим энергопотреблением и высокой устойчивостью к снижению напряжения питания, что критично для устройств на батарейках или ограниченных в энергоресурсах. Кроме того, в сравнении с подобными стохастическими байесовскими машинами, логарифмическая архитектура показала лучшие характеристики по энергопотреблению и задержкам при работе с непростыми моделями, где присутствует большое количество состояний с низкой вероятностью. В задачах распознавания жестов, где вероятность событий более равномерно распределена, стохастические методы также обладают преимуществами по энергоэффективности, особенно при выборе режима работы с динамической остановкой вычислений. Тем не менее, именно в сложных, зависимых во времени моделях логарифмическая машина становится незаменимым решением.

Техническая реализация устройства основана на сочетании CMOS-логики и массивов мемристоров, интегрированных в бэкенде кристалла. Особое внимание уделяется архитектуре считывания данных из памяти, использующей двухтранзисторно-два-мемристорный (2T2R) ячейковый дизайн, обеспечивающий высокую надежность хранения информации и подавление ошибок, сопоставимое с современными проверками и коррекцией ошибок. Для определения состояний мемристоров применяется дифференциальный предусилитель с предварительным зарядом, что повышает чувствительность и надежность при динамическом изменении напряжения питания. Параллельно с созданием аппаратной базы, была проведена масштабная программная эмуляция и верификация алгоритмов работы логарифмической байесовской машины, что позволило подтвердить стабильность и масштабируемость концепции для более сложных и объемных задач, выходящих за рамки прототипа. Эти исследования включали расчеты энергозатрат, оценку точности в реальных сценариях и устойчивость к ошибкам, возникающим из-за вариабельности параметров мемристоров и электроники.

Уникальность логарифмической мемристорной байесовской машины заключается в том, что она объединяет преимущества двух миров: точность и объяснимость байесовских моделей с эффективностью и скоростью цифровых вычислений, дополнительно при этом существенно снижая энергозатраты и задержки. В эпоху нарастающей потребности в интеллектуальных устройствах с долговременной автономной работой и ограниченными ресурсами, данные решения становятся ключевыми для развития индустрии периферийных вычислений, Интернета вещей и ориентированных на человека приложений. Перспективы дальнейшего развития этого направления включают создание масштабируемых систем с поддержкой более сложных вероятностных моделей и глубокой иерархической структурой зависимостей, оптимизацию аппаратной части с использованием новейших технологий памяти и тонкопленочных материалов, а также интеграцию с другими типами вычислительных элементов, включая квантовые и спинтронные устройства. Помимо чисто технических улучшений, важным направлением является разработка универсальных инструментов и библиотек для проектирования и обучения таких машин, что позволит значительно расширить область их применений. В резюме, логарифмическая мемристорная байесовская машина представляет собой значимый шаг вперед в создании энергоэффективных, точных и прозрачных вычислительных устройств для анализа и принятия решений в условиях неоднозначных и сложных данных.

Ее потенциал особенно проявляется в задачах периферийных вычислений и встроенного искусственного интеллекта, где критически важны низкое энергопотребление и высокая надежность. Благодаря своим уникальным архитектурным решениям и интеграции с современными технологиями памяти, она открывает новые горизонты для интеллектуальной обработки сигналов, медицинской диагностики, сенсорных систем и многих других сфер, требующих качественного управления неопределенностью и принятия решений в реальном времени.