В современном мире высокоскоростных цифровых технологий проектирование микросхем стало невероятно сложным и многогранным процессом. Среди множества инструментов, обеспечивающих качество и надежность конечных устройств, особое место занимает статический анализ временных характеристик, или STA (Static Timing Analysis). Многие знакомы с названиями таких инструментов, как Synopsys PrimeTime или Cadence Tempus, но немногие знают, как эти системы на самом деле работают и почему без них невозможна успешная верификация цифрового дизайна. STA — это ключевой этап в процессе разработки чипов, цель которого — удостовериться в том, что все временные параметры проекта соответствуют заданным требованиям. Дело в том, что в мире электронных микросхем время — это одна из самых важных величин.

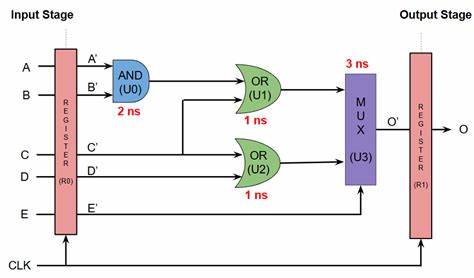

Каждый транзистор, каждый элемент логики и путь, по которому движется сигнал, обладают собственными задержками. Эти задержки могут привести к тому, что информация не успеет вовремя достигнуть конечного элемента, что вызовет сбой в работе всей системы. Изначально концепция статического анализа временных характеристик строилась на методах, подобным Program Evaluation and Review Technique (PERT), применявшимся в управлении проектами для выявления критического пути и вычисления запаса времени. В цифровом проектировании STA применяется для поиска самых длинных и коротких временных путей в схеме, которые должны обязательно удовлетворять условиям стабильности данных. Главным вызовом STA является то, что этот анализ происходит на ранних этапах разработки, когда физический вид микросхемы еще не определен.

Нет никакой возможности точно знать, как именно будут располагаться транзисторы и связи между ними. Несмотря на это, инструменты STA располагают обширными библиотеками компонентов с заранее измеренными или моделированными задержками — так называемыми "Cell Libraries". На основании этих данных и алгоритмов, учитывающих различные параметры, STA может с высокой точностью прогнозировать задержки в цепях. В основе работы статического анализа лежит понятие синхронизации. В цифровых схемах синхронизация означает, что все изменения сигналов происходят в определенные моменты времени, управляемые тактовым сигналом.

Без синхронизации расчет правильности работы схемы становится невозможен, ведь можно получить противоречивые сигналы на выходах. Чтобы обеспечить правильность работы, данные должны стабилизироваться и храниться в специальных элементах — регистрах, которые сохраняют значения во время определенного тактового импульса. Каждый регистр предъявляет свои требования к входным сигналам и времени их стабильности. Среди таких требований выделяют понятия setup time и hold time. Setup time — это минимальное время, в течение которого данные на входе регистра должны оставаться неизменными до тактового события (например, положительного фронта тактового сигнала), чтобы данные были успешно записаны.

Hold time — минимальное время, в течение которого данные должны оставаться стабильными после тактового события. Нарушение любого из этих условий приводит к сбоям и ошибкам, которые STA призвана выявить. Регистры сами по себе имеют задержки — как в передаче данных, так и во влиянии тактового сигнала. Эти задержки необходимо учитывать отдельно, поскольку они влияют на время доставки информации по пути и на корректность анализа всего дизайнерского решения. Инструмент STA импортирует все данные о задержках из библиотек и производит выверенный расчет для каждого пути добавления задержек и сопоставления их с требованиями синхронизации.

Одной из основных задач STA является вычисление "Slack" — это запас времени между фактическим временем поступления сигнала и моментом, к которому он должен быть стабилен согласно setup time. Если slack положительный, значит схема работает с запасом, если же он отрицательный — в цепи обнаружено нарушение времени, что необходимо исправить. Особое внимание STA уделяет не только setup time, но и hold time violations. Зачастую это более сложные для исправления ошибки, так как их причиной бывают слишком короткие пути — то есть сигнал достигает регистра раньше, чем старые данные успеют сохраниться. Поэтому инструменты анализа предлагают способы устранения таких задержек, например, путем вставки буферов сигналов или перераспределения логики.

Значение STA нельзя переоценить. Несмотря на кажущуюся невидимость и относительно невысокий "гламур" по сравнению с инструментами синтеза или проектирования, это именно тот этап, который не допускает дорогостоящих ошибок, способных уничтожить месяцы или даже годы работы. Внедрение STA позволяет проектировщикам получить ясную картину реальных временных характеристик и обеспечить, что чип будет функционировать корректно на заданной тактовой частоте. Современные инструменты STA интегрированы в сложные цепочки автоматизации проектирования (EDA) и взаимодействуют с синтезом, Floorplanning, Placement & Routing, Power Analysis и другими этапами, образуя единый процесс, направленный на максимальную оптимизацию и качество разрабатываемого кремния. Понимание принципов работы STA и правильное использование его результатов значительно упрощают жизнь инженеров и повышают вероятность успеха проекта.

Стоит также отметить, что STA широко используется не только в плане классического хронотехнического анализа на этапе верификации, но и как база для обнаружения потенциальных проблем в новых технологиях, моделирования новых архитектурных идей и оптимизации энергопотребления. Таким образом, STA — это неотъемлемый элемент современного цифрового проектирования, без которого ни один чип не станет надежным. Почему же, несмотря на столь важную роль, STA остается менее популярным и «невидимым» инструментом? Все очень просто — пользователи привычно сосредотачиваются на разработке функциональности и синтезе логики, тогда как временные характеристики воспринимают как что-то второстепенное, что "сама собой решится". Такой подход нередко приводит к тому, что проект доходит до физического исполнения с негативными сюрпризами: несоответствие временным ограничениям, нестабильная работа, ошибки сигнальных цепей. Именно в этот момент значение STA наконец осознается в полной мере.

Для инженера и проектировщика понимание истории и принципов работы статического анализа временных характеристик откроет глаза на важность проверки каждой цепи и каждой задержки, внесет дисциплину в процесс проектирования и позволит избегать распространенных ошибок. Кроме того, глубокие знания STA позволяют более эффективно взаимодействовать с инструментами автоматизации, быстро устранять проблемы и оптимизировать архитектуру. В итоге можно сказать, что STA — это не просто набор вычислений и проверки условий. Это философия проектирования, понимание законов физического мира электроники и проявление фундаментальных принципов инженерии. Без STA высокотехнологичные микросхемы не смогли бы работать корректно и эффективно.

Поэтому каждый, кто стремится к созданию успешного цифрового дизайна, должен познакомиться с этим инструментом поближе и научиться доверять его "голосу" — голосу времени в мире электронных схем.