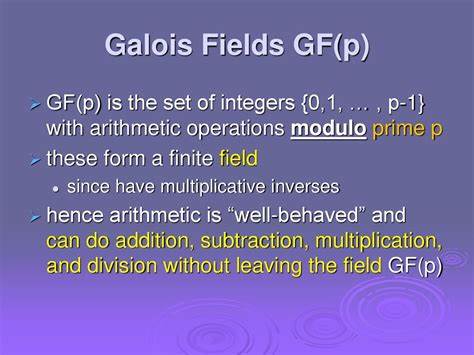

Процессоры, выпущенные в 2021 году, получили ряд новых возможностей, которые значительно расширяют спектр вычислительных задач, доступных для высокопроизводительного и эффективного исполнения. Одной из таких возможностей стали инструкции для работы с полями Галуа — математическим аппаратом, важным для криптографии, кодирования и обработки данных. Эти инструкции позволяют аппаратно эффективно выполнять операции в конечных полях GF(2^n), где n — это размерность поля, например 8, 16, 32 или 64 бита. В итоге это открывает новые горизонты для ускорения алгоритмов, опирающихся на арифметику в конечных полях, что особенно востребовано в системах защиты информации и при обработке ошибок. Первоначально процессоры традиционно работают с целочисленными типами данных типа uint8_t, uint16_t, uint32_t и uint64_t, которые можно рассматривать как целые числа по модулю 2^8, 2^16, 2^32 и 2^64 соответственно.

При таких ограничениях операции сложения и умножения сводятся к арифметике по модулю 2^n, где добавление и умножение легко реализуются как обычные операции с последующим отсечением старших бит. Однако такая форма редукции, основанная на степенях двойки, хоть и проста с аппаратной точки зрения, не обладает некоторыми важными математическими свойствами, например, существованием мультипликативной обратной для каждого ненулевого элемента. Это критично для криптографии и многих алгоритмов, где требуется вычислять обратные элементы и работать с полями, обладающими структурой полноценного поля Галуа. Чтобы исправить эту некорректность с математической точки зрения и сохранить эффективность исполнения, были разработаны подходы, в основе которых лежат операции с многочленами над полем GF(2). В данном подходе двоичные битовые строки интерпретируются как коэффициенты многочленов от переменной x, и операции выполняются в виде сложения и умножения многочленов с последующей редукцией по неприводимому многочлену определённой степени.

Выбор именно неприводимого многочлена — ключевой момент, поскольку он определяет, что поле Галуа является полем, а не просто кольцом, что гарантирует существование всех обратных элементов. Классические неприводимые многочлены для размерностей 8, 16, 32 и 64 бит выглядят так: x^8 = x^4 + x^3 + x + 1, x^16 = x^5 + x^3 + x + 1, x^32 = x^7 + x^3 + x^2 + 1 и x^64 = x^4 + x^3 + x + 1. Благодаря этим формулам возведение степеней x в более высокие степени сводится к линейной комбинации более низких степеней, что позволяет эффективнее реализовывать операцию редукции в многочленах. В реальных системах операции сложения в таких полях на практике сводятся к применению операции XOR по разрядам, что чрезвычайно быстро реализуется аппаратно на современных процессорах. Однако умножение и вычисление обратных элементов требуют более сложных вычислений либо использования таблиц поиска.

Для полей с меньшей размерностью, например GF(2^8), одним из классических решений остаётся применение таблиц. Таблицы размером 256 на 256 для умножения занимают определённый объём памяти, но позволяют выполнять умножение за одну операцию с помощью индексирования. Хотя достаточно большой размер, он ещё вполне применим в современном оборудовании. Для вычисления обратного элемента можно использовать отдельную таблицу размером 256, позволяющую быстро получить необходимые инверсные элементы. В случае более крупных полей, таких как GF(2^16), размеры таблиц многократно увеличиваются, что уже становится проблематично для большинства систем, а для GF(2^32) и даже GF(2^64) использование полных таблиц становится невозможным — их объём превосходит доступную оперативную память.

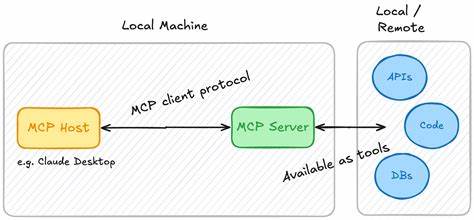

Для повышения производительности на таких больших полях современные процессоры предлагают специализированные инструкции, которые аппаратно реализуют необходимые операции над многочленами. Например, процессоры архитектуры x86/x64 поддерживают инструкцию pclmulqdq, которая позволяет умножать два 64-битных многочлена и получать 128-битный результат. В инструкции используется 128-битный регистр XMM, что позволяет выбирать старшие или младшие 64-битные половины операндов. Аналогичные инструкции присутствуют и в ARM64, такие как pmul, pmull и pmull2, позволяющие ускорять вычисления многочленов различной битности в SIMD-формате. Именно благодаря таким аппаратным возможностям появилась возможность реализовывать операции умножения и обратных элементов прямо в CPU без использования громоздких таблиц, значительно ускоряя работу с конечными полями большой размерности.

Реализация умножения в GF(2^64) сводится к последовательному выполнению операции бесконечной точности умножения многочленов, применению редукции по выбранному неприводимому многочлену и использованию команды XOR для комбинирования промежуточных результатов. Например, по полиному x^64 = x^4 + x^3 + x + 1 редукция может быть выполнена с помощью нескольких вызовов pclmulqdq и операций XOR. Популярная реализация операции умножения в таком поле выглядит компактно и эффективно с точки зрения программного кода и аппаратного исполнения. Кроме того, для вычисления обратных элементов в GF(2^64) возможно использовать метод возведения в степень по правилу Ферма, реализуемый через многократное умножение, что избавляет от необходимости вычислять обратные элементы напрямую или хранить их в таблицах. Стоит отметить, что для полей среднего размера, таких как GF(2^32), возникает дополнительный вызов в части реализации редукции, поскольку инструкции процессора заточены под работу с 64-битными операндами, и сдвиг на 32-бит необходимо делать вручную с использованием дополнительных приемов, таких как шифрования или перестановки байтов.

Из интересных особенностей современного оборудования стоит выделить появление в последних процессорах Intel набора инструкций GFNI (Galois Field New Instructions), в частности команды gf2p8mulb, которая непосредственно реализует умножение в GF(2^8) с использованием неприводимого многочлена x^8 = x^4 + x^3 + x + 1. Эта инструкция доступна на разных уровнях SIMD и обеспечивает параллельную обработку множества значений одновременно, что существенно ускоряет операции умножения в криптографии и кодировании на аппаратном уровне. Дополнительные инструкции gf2p8affineqb и gf2p8affineinvqb реализуют операции аффинных преобразований и вычисления инверсных элементов с возможностью задания с помощью масок и констант произвольных битовых трансформаций, что расширяет инструментарий для создания сложных и эффективных алгоритмов. Для случаев, когда необходимо умножать большое количество значений на постоянный коэффициент в GF(2^8), удачным подходом является разбиение операнда на старшие и младшие полубайты и использование небольших таблиц размером всего 16 элементов для каждого полубайта. Такие таблицы могут быть загружены непосредственно в SIMD регистры, а выбор элементов реализован через инструкции pshufb (AMD64) или tbl (ARM64), позволяя выполнять несколько параллельных операций быстро и без обращений к памяти.

Эта техника широко используется в современных библиотеках, например, Intel ISA-L, для обеспечения высокой производительности при работе с конечными полями в задачах хранения данных и криптографии. В итоге, появление и развитие аппаратной поддержки арифметики в полях Галуа на процессорах 2021 года является важным технологическим шагом для повышения эффективности сложных вычислений, применимых в криптографии, защите данных, сетевых протоколах и системах коррекции ошибок. Совмещение математической строгости с аппаратной оптимизацией обеспечивает значительный прирост скорости и снижение затрат ресурсов, что актуально для современных и будущих вычислительных систем. Понимание этих возможностей и грамотное использование соответствующих инструкций открывает широкие перспективы для программистов, инженеров и исследователей, работающих с высокоскоростными вычислительными задачами и обеспечением безопасности информации.