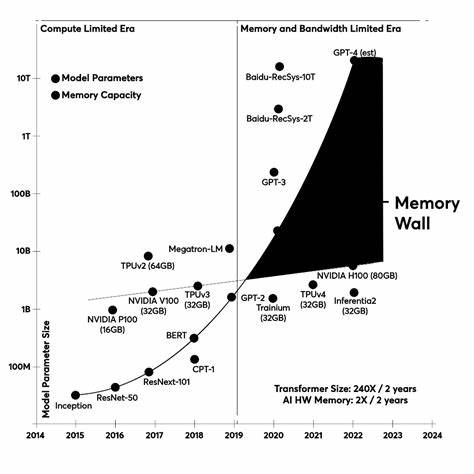

В современном мире информационных технологий оперативная память играет ключевую роль в обеспечении быстрого и эффективного выполнения вычислительных задач. Однако отрасль столкнулась с серьезным препятствием, которое называют «стеной памяти». Этот термин отражает критическое замедление масштабирования и улучшения технологий динамической оперативной памяти (DRAM), что создает бутылочное горлышко для развития вычислительной техники, особенно в условиях стремительного роста искусственного интеллекта и больших данных. Исторически Moore’s Law, сформулированный в 1965 году Гордоном Муром, предсказал удвоение количества транзисторов на кристалле каждые 18-24 месяца. Это правило стало фундаментом развития как логических интегральных схем, так и памяти DRAM.

В период расцвета DRAM плотность хранения данных увеличивалась в два раза примерно каждые полтора года. Это позволяло добиться огромных улучшений в объеме памяти и снижении стоимости за бит. Однако в последние десять лет темпы роста плотности DRAM существенно замедлились. Сейчас прирост составляет лишь около 2х за десятилетие, что значительно уступает прошлым стандартам и даже опережающему развитие логических процессоров. Это обусловлено рядом технологических особенностей DRAM, таких как сложность дальнейшего уменьшения размеров ячеек памяти, трудности с поддержанием стабильности и надежности при экстремальной миниатюризации, а также ограничения архитектуры памяти.

Базовая структура DRAM описывается как сетка из ячеек, каждая из которых содержит один транзистор и один конденсатор (1T1C). Транзистор контролирует доступ к ячейке, а конденсатор хранит электрический заряд, отражающий битовую информацию. Характерной особенностью DRAM является необходимость регулярного обновления заряда (refresh), поскольку конденсаторы со временем теряют энергию. Этот процесс требует дополнительных ресурсов и вносит сложность в управление памятью. Одним из основных ограничителей масштабирования является конденсатор.

Чтобы сохранить емкость, он должен иметь очень высокое соотношение высоты к площади (100:1). Изготовление таких структур с точностью до нескольких нанометров требует предельного контроля на всех этапах производства, включая сложные процессы травления и нанесения сверхтонких диэлектрических слоев. Аналогично, усилительные схемы – sense amplifiers – сталкиваются с проблемами при уменьшении размеров: чем меньше ячейка, тем слабее сигнал для считывания, что повышает вероятность ошибок и влияет на стабильность. Современная DRAM индустрия разделена на несколько ключевых типов памяти, каждый из которых ориентирован на определенные сферы применения. DDR5 обеспечивает максимальное количество памяти и используется в серверных решениях.

LPDDR5X – оптимизирован для низкого энергопотребления и применяется в мобильных устройствах и специализированных процессорах. GDDR6X ориентирован преимущественно на графические задачи и игровые системы, а HBM (High Bandwidth Memory) воплощает высший уровень производительности и пропускной способности, необходимый для ускорителей и систем искусственного интеллекта. HBM отличается как широкой шиной данных (до 1024 бит) и вертикальным объемным расположением микросхем памяти, так и высокой стоимостью. Из-за необходимости многослойного стэкинга с использованием технологий TSV (сквозных соединений через кристалл) цена на такой тип памяти в несколько раз превышает стоимость обычных DDR5 модулей. Дополнительно создает сложности высокая сложность производства, низкая выходная годность и требования к точному позиционированию множества слоев.

С ростом искусственного интеллекта и моделирования огромных нейросетей требования к объему и скорости памяти стремительно возрастают. К примеру, современные модели требуют многотерабайтного пространства для хранения весов нейросетей, что приводит к взрывному росту спроса на HBM. При этом расходы на память могут составлять до 60% стоимости производства высокопроизводительных ускорителей нового поколения, что подчеркивает глубину вызова, с которым столкнулась индустрия. В ответ на эти вызовы отрасль приступила к поиску решений, способных преодолеть «стену памяти». Одним из краткосрочных подходов является переход к 4F2 макету ячейки с использованием вертикальных транзисторов.

Такая архитектура позволяет уменьшить занимаемую площадь, повышая плотность хранения без дальнейшего уменьшения базового технологического узла, который становится все более технологически и экономически сложным. В долгосрочной перспективе серьезные изменения могут принести 3D DRAM – объемное размещение ячеек и сенсорных усилителей, интеграция дополнительных слоев логики и памяти. Эти технологии обещают не только увеличение плотности, но и снижение энергоемкости операций, улучшение пропускной способности и снижение стоимости на гигабайт памяти. Параллельно ведутся разработки и новых типов памяти. Среди перспективных направлений – фероэлектрическая память (FeRAM), магниторезистивная память (MRAM) и другие «восходящие» технологии, которые в перспективе могут заменить или дополнить традиционную DRAM.

Они обладают преимуществами в энергоэффективности, неволатильности и скорости, но сталкиваются с собственными технологическими и производственными проблемами. Еще одним революционным направлением является Compute-In-Memory (CIM) – концепция интеграции вычислительных возможностей непосредственно в память. Текущая архитектура DRAM требует обширной коммуникации с центральным процессором для обработки команд, что ведет к значительным накладным расходам на передачи данных. CIM предлагает перенесение вычислительной логики ближе к данным, позволяя проводить операции напрямую в ячейках памяти или близко к ним, сильно снижая задержки и энергопотребление. Для реализации CIM необходимо внедрение встроенной логики управления в память, что пока сложно с технологической точки зрения и противоречит экономическим моделям производства традиционной DRAM.

Однако совместные усилия крупных производителей и стартапов показывают значительный прогресс. В частности, идея использования специализированных интерфейсов и чиплетов с вычислительными модулями в составе многоуровневых стеков памяти становится все более реальной. Текущее поколение HBM, а также предстоящие HBM4 и последующие поколения, используют различные инновации в упаковке, такие как гибридное бондинг (hybrid bonding), позволяющее устранять зазоры между слоями, улучшать теплоотвод и снижать энергопотребление. Также идея внедрения базовых логических кристаллов (base dies) с функциями управления и коммуникаций уже применяется производителями, что открывает дверь для масштабирования архитектур CIM. Другим перспективным направлением является стандартизация более быстрых и энергоэффективных интерфейсов, таких как UCIe (Universal Chiplet Interconnect Express) и специализированные протоколы вроде Nulink, применяемые стартапами.

Они позволяют расширить пропускную способность, снизить энергопотребление и повысить плотность интеграции, что крайне важно для уменьшения влияния коммуникационных задержек между процессорами и памятью. На фоне все этого складываются новые конкурентные условия в отрасли памяти. Топовые производители, включая Samsung, SK Hynix и Micron, вложили значительные средства в разработку передовых DRAM и HBM технологий. Однако проблемы с выходной годностью, сложностью производства и растущими затратами подталкивают к переоценке архитектурных подходов и усилению сотрудничества с партнерами из сферы логики и упаковки. Впрочем, несмотря на все сложности, потенциальные выгоды очень велики.

Преодоление «стены памяти» не только позволит создавать более мощные и эффективные вычислительные системы, но и станет катализатором развития таких направлений, как искусственный интеллект, большие данные, высокопроизводительные вычисления и мобильные устройства следующего поколения. Таким образом, «стена памяти» — это не просто технологический вызов, а трансформационный этап для всей индустрии микропроцессоров и памяти. От успешного преодоления этого барьера зависит дальнейшее ускорение инноваций, развитие новых архитектур и возможность удовлетворить растущие запросы пользователей и приложений во всем мире.