Современная индустрия полупроводников находится на пороге очередного технологического рывка, где интеграция новых архитектур и производственных методов меняет привычные отраслевые стандарты. Среди наиболее обсуждаемых тем выделяются последние работы Intel над процессом 18A, эволюция DRAM от классической 6F2 к 4F2 и 3D решениям, а также применение технологии Backside Power, предлагающей новый взгляд на питание кристаллов. Подробный анализ этих направлений позволяет лучше понять, куда движется отрасль, какие сложности предстоит преодолеть и какие перспективы открываются перед производителями и конечными пользователями. Начать стоит с технологии Intel 18A — одного из самых ожидаемых этапов в развитии передовых литографических процессов. Она отметилась переходом от классических finFET к Gate-All-Around (GAA) архитектуре с использованием широких риббонов.

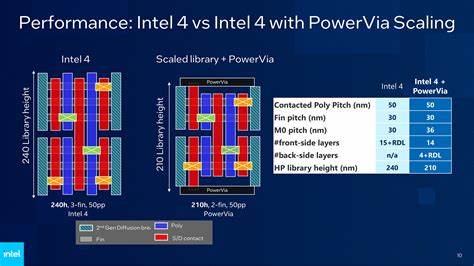

Такой шаг приносит значительное уменьшение площади ячейки SRAM, заявляется сокращение порядка 30% по сравнению с предыдущим процессом Intel 3. Эта оптимизация напрямую связана с эффективным использованием пространства, что становится критичным при постоянном стремлении к увеличению плотности интеграции и снижению энергопотребления. Сложности перехода на 18A связаны не только с новым типом транзисторов, но и с внедрением backside power delivery, технологии питания через обратную сторону кристалла. Данный подход радикально меняет способ подачи электричества, позволяя снизить падение напряжения и уменьшить паразитное сопротивление, что позитивно сказывается на стабильности и производительности. Intel впервые в широком масштабе демонстрирует рабочее применение такой технологии, но при этом отмечает, что её внедрение требует серьёзных изменений в изготовлении полупроводников: необходима высокая точность обработки обратной стороны, интеграция новых материалов и оборудования для обеспечения надёжности и высокого выхода продукции.

Параллельно с развитием процессов логики, важное значение имеет прогресс в области DRAM. Классическая архитектура 6F2, представлявшая собой промышленный стандарт на протяжении многих лет, начинает терять эффективность при масштабировании на углеродном уровне 1d и ниже. Сложности связаны с уменьшением контактных площадей ячеек памяти, что усложняет обеспечение надёжного соединения между транзистором и конденсатором. Кроме того, возросшее сопротивление внутри элементов негативно влияет на скорость работы и читаемость информации. Решением этих проблем в отрасли рассматриваются два основных направления — инновационный 4F2 и 3D DRAM.

Архитектура 4F2 подразумевает использование вертикального канального транзистора, что значительно уменьшает длину тока и сопротивление, обеспечивая более эффективную работу ячейки при сохранении плотности размещения. Эта технология требует высокоточных процессов травления и осаждения, поскольку компоненты отличаются высокой степенью аспекта, что долгое время было техническим барьером для внедрения. Однако сейчас, благодаря развитию инструментальной базы и материалов, 4F2 становится реальной альтернативой и перспективным этапом в эволюции памяти. Одновременно развивается направление 3D DRAM, которое предлагает многослойное наращивание ячеек памяти, позволяя преодолеть ограничения масштабирования в плоскости. Китайские производители проявляют особенный интерес к этому подходу, так как он снижает зависимость от самых продвинутых литографических технологий, что делает производство более доступным в условиях ограничений на импорт оборудования.

3D архитектура открывает пути для значительно большей плотности, но одновременно требует сложной интеграции межслоевых соединений и решения вопросов теплового управления. Особое внимание уделяется и гибридным подходам, таким как использование периферии под ячейками (peri-under-cell) и комбинация с бексайд питанием, что наряду с применением гибридного бондажа и других инноваций позволяет продвигать технологии к индустриальному уровню с хорошей окупаемостью и высоким качеством продукции. Тем не менее, каждая из этих технологий сопряжена с вызовами: стоимость разработки и внедрения высока, дорожат процессами получения стабильных выходов продукции, а также оптимизацией дизайна под новые архитектуры. Ещё одним не менее важным аспектом развития полупроводников является усиление роли цифровых двойников фард и симуляционных технологий на атомном и вафельном уровне. Сложность современных транзисторов и интегральных схем требует использования виртуальных прототипов, позволяющих ускорить разработку и снизить испытательные расходы.

Использование машинного обучения и ускоренных квантовых моделей позволяет получать точную информацию о поведении материалов и процессов на очень мелком уровне, что значительно повышает вероятность успешного внедрения инноваций в производство. Вместе с этим растёт значимость новых архитектур транзисторов, таких как forksheet и stacked CFET. Forksheet предлагает более плотное размещение NMOS и PMOS с минимизацией паразитной ёмкости, но требует нового класса ультранизкой диэлектрической изоляции и высокоточного нанесения слоёв. CFET, в свою очередь, развивается как следующий после GAA шаг, предполагающий вертикальную интеграцию транзисторов с возможностью значительного повышения плотности при условии преодоления технологических и экономических барьеров. Несмотря на перспективы, эти решения ещё далеки от массового производства и требуют не менее десяти лет до выхода в индустриальный масштаб.

Важным элементом обсуждения в отрасли становится китайская разработка FlipFET. Этим инновационным методом предлагается создавать транзисторные структуры с двухсторонним расположением активных компонентов через переворачивание вафель и поэтапную обработку обеих сторон. Дизайн FlipFET обещает упрощение интеграции при сохранении высокого уровня производительности и энергоэффективности, но метод сильно зависит от точности совмещения слоёв и ограничен повышенными затратами на многоступенчатые процессы обработки. Тем не менее, если эти вызовы будут успешно преодолены, технология может послужить основой для создания многоуровневых транзисторных стэков и стать серьёзным конкурентом другим CFET-решениям. Что касается стоимости, то внедрение новых передовых процессов, таких как Intel 18A с backside power, естественно влечёт рост себестоимости продукции на начальных этапах.

Это связано не только с дорогим оборудованием, но и с необходимостью глубокой перестройки производственных линий, а также увеличением времени цикла изготовления изделий. Однако масштабы экономии, получаемой за счёт повышения плотности размещения, повышения тактовых частот и понижения энергопотребления, делают такие инвестиции оправданными в долгосрочной перспективе, особенно при конкуренции за лидерство на рынке высокопроизводительных вычислительных систем и мобильных устройств. Подытоживая, цифровая революция в полупроводниковых технологиях не стоит на месте. Инновации в логических процессах, таких как Intel 18A с новой архитектурой транзисторов и backside power, дополняются параллельной эволюцией памяти DRAM, где 4F2 и 3D технологии открывают новые границы плотности и эффективности. Применение цифровых двойников и передовых симуляций позволяет снизить риски и ускорить вывод продуктов на рынок.

В то же время, амбициозные проекты, включая китайский FlipFET и гибридные архитектуры, демонстрируют желание отрасли пробовать новые пути интеграции и оптимизации. Несмотря на высокие затраты и технические барьеры, всё это формирует базу для ближайшего десятилетия, в котором технологии полупроводников будут становиться ещё более компактными, производительными и энергоэффективными, поддерживая развитие цифровой экономики и инноваций во всех сферах жизни.