Проект 486Tang представляет собой впечатляющее достижение в мире цифровой электроники и любителей ретро-вычислительной техники. Его цель - запустить процессор Intel 486 на компактной FPGA плате размером с кредитную карту, а именно Sipeed Tang Console 138K. Это не просто инженерная игрушка, а настоящий рабочий классический ПК, воплощённый в современном FPGA-устройстве, обладающий архитектурой, позволяющей запускать операционную систему DOS и классические приложения эпохи 486 процессоров. Ценность проекта 486Tang заключается в портировании ядра ao486 - уже известного и зрелого проекта эмуляции процессора i486, изначально разработанного для FPGA платформы MiSTer PC, использующей Altera FPGA. Автор проекта добился уникального результата - портировал это ядро в совершенно другую архитектуру FPGA, Gowin GW5A, используемую в Sipeed Tang Console 138K.

Этот факт особенно значим, потому что до этого ao486 не запускался на неплатформах Altera, что подчёркивает сложность адаптации современного кодекса с множеством высокопроизводительных функций для совершенно другой аппаратной среды. Одним из ключевых моментов в доработке и адаптации стала работа с памятью. Оригинальная платформа MiSTer использует DDR3 для работы основной памяти, однако в проекте 486Tang выбран SDRAM, которую было проще интегрировать в систему и удобнее с точки зрения времени взаимодействия с процессором. SDRAM на Tang Console - 16-битная, в то время как ao486 ожидает 32-битные обращения, что обычно означает задержку в один цикл. Автор сумел решить эту проблему, удвоив частоту работы контроллера памяти, что позволяет делать 32-битные операции за один такт, благодаря технологии, известной как "double-pumping".

Следующим вызовом стала организация доступа к дисковому пространству. В классических системах MiSTer ядро forward'ит запросы IDE к встроенному ARM процессору с быстрым интерфейсом связи, который служит прослойкой для работы с образами дисков. Платформа Tang не имеет подобных возможностей передачи больших объёмов данных с МК к FPGA, располагая лишь слабым UART-интерфейсом. Решение - использовать SD-карту непосредственно как источник и хранилище данных для диска. Для запуска системы была разработана особая загрузочная подсистема, которая считывает BIOS, VGA BIOS, CMOS-настройки и данные команды IDE IDENTIFY из первых 128 КБ SD-карты и помещает их в память, обеспечивая полноценный старт системы.

Одним из наиболее сложных этапов работы стала отладка и bring-up системы. Запуск полноценной системы с процессором i486 - задача гораздо более комплексная, чем работа с более простыми игровыми платформами. Сам модуль процессора ao486 состоит из более чем 25 тысяч строк кода на Verilog, что значительно усложняет диагностику. Для ускорения и упрощения отладки автор применил Verilator - мощный инструмент для симуляции систем на аппаратном уровне, который позволил запускать полную загрузку операционной системы DOS в эмуляции за считанные минуты. Благодаря тому, что BIOS использует механизм вывода отладочных сообщений через порт 0x8888, можно оперативно получать важные логи и отслеживать процесс загрузки и возможные ошибки.

Опыт работы с FPGA и симуляторами показал, насколько полезна такая двойная стратегия разработки: быстрая отладка на симуляторе и последующая проверка на реальном оборудовании. Многие баги и узкие места были выявлены именно в процессе симуляции - от нехватки регистров для pipeline до особенностей поведения переменных внутри FPGA. Разработчик смог быстро изолировать и исправить критические ошибки, оптимизируя ядро для аппаратной платформы. Проект выделяется и на уровне производительности. Изначально диспетчерская частота FPGA Sipeed Tang Console не позволяла достичь высоких скоростей, и производительность системы была близка к уровню 80386 с частотой около 25 МГц.

Чтобы улучшить показатели, пришлось детально исследовать узкие места вычислительного конвейера и архитектуры. Были оптимизированы цепочки комбинированной логики, переработаны длинные пути и внесены улучшения в механизм сброса сигналов, что позволило сократить задержки на нескольких критических участках. Особое внимание уделялось решению проблем с fetch-декодером инструкций. Архитектура x86 известна сложной обработкой команд переменной длины и вычислением эффективных адресов, что нередко снижает максимальный тактовый диапазон. Для повышения частоты была реализована оптимизация в вычислении размера управляемого буфера в fetch-юните, которая позволила минимизировать критический путь и была проведена с допустимыми компромиссами по эффективности, в итоге практически не влияя на производительность с точки зрения CPI.

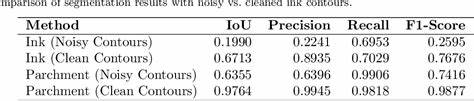

Требуется также упомянуть оптимизацию работы буфера преобразования виртуальных адресов Translation Lookaside Buffer (TLB). Первоначально использовалась полностью ассоциативная структура с 32 позициями, что создавало длинные и медленные пути в логике. В рамках улучшения производительности TLB был преобразован в 4-канальный set-associative кеш, который легче реализовать и который лучше подходит для нагрузок DOS, где высокая степень виртуализации памяти не требуется. В результате в тестах Landmark 6 существующая система показала улучшение производительности порядка 35% и приблизилась по возможностям к компьютеру 486SX-20. Это впечатляющий результат, учитывая аппаратные ограничения платформы Tang.

Проект 486Tang не просто доказывает, что FPGA размером с кредитную карту способны запускать полноценные x86 системы, он помогает лучше понять архитектурные тонкости процессоров 486 класса и сложности их воспроизведения на современном оборудовании. Работа с FPGA открывает возможности для изучения архитектуры компьютеров на низком уровне, доступные не только профессионалам, но и энтузиастам и любителям ретро-техники. Сравнение работы с x86 и ARM архитектурами также стало важным опытом для автора. x86 остаётся самым сложным из ныне существующих процессоров с невероятным количеством инструкций, режимов адресации и особенностей, что с одной стороны делает его гибким и совместимым со всем существующим ПО, а с другой - создаёт огромную нагрузку на разработчиков ядер на FPGA. Классические архитектуры с фиксированной длиной инструкций, как ARM7 и подобные, продолжают быть привлекательными для создания лёгких и эффективных реализаций, которые проще отлаживать и масштабировать.

Портирование ao486 стало шагом в расширении границ возможного и демонстрацией того, как можно работать с самой сложной архитектурой в мире процессоров на малогабаритной FPGA платформе. 486Tang - это не только технический эксперимент, но и демонстрация синергии оригинальных решений и классических архитектур в рамках компактного и доступного аппаратного решения. В перспективе подобные проекты могут получить широкое распространение, позволив запускать классические операционные системы и программы на современных портативных FPGA-платформах, вдохнув вторую жизнь в ретро-компьютинг и развивая публичное понимание микроархитектур. Значение 486Tang подчеркнуто его открытостью: исходный код доступен на GitHub, что даёт всем возможность изучить, модифицировать и использовать этот удивительный проект. Он открывает двери для новых исследований в области FPGA-эмуляции, способствует развитию знаний о внутренностях процессоров Intel и вдохновляет хобби-энтузиастов по всему миру.

В итоге данный проект является уникальным мостом между эпохой классических ПК и современным миром FPGA, объединяя опыт инженеров прошлого века с инновациями цифрового проектирования XXI века. 486Tang - яркий пример того, как техническое творчество и упорство позволили создать настоящий x86 компьютер размером с кредитную карту, способный показать, что будущее ретро-технологий по-настоящему мобильное и универсальное. .