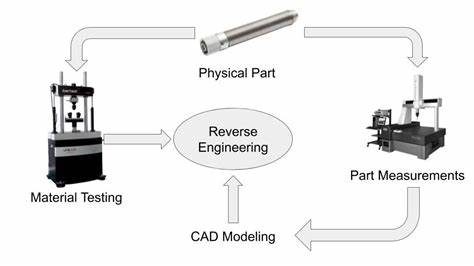

Современные микроконтроллеры с программируемой логикой становятся незаменимыми в разнообразных электронных проектах, требующих гибких и эффективных решений. Особенно интересным компонентом в этом контексте является Configurable Logic Block (CLB) от Microchip, предназначенный для реализации пользовательской логики внутри самого микроконтроллера. Для более глубокого понимания его возможностей и структуры целесообразно провести реверс-инжиниринг CLB, начиная с изучения базовых логических элементов (Basic Logic Elements, BLE). CLB представляет собой блок, состоящий из 32 BLE, каждый из которых основан на таблицах истинности четвертого порядка (4-LUT). LUT — это основа программируемой логики в FPGA и подобных устройствах, благодаря которой возможно построение любых булевых функций с четырьмя входами.

Каждая LUT принимает четыре входных сигнала и выдаёт один логический выход, позволяя реализовать разнообразные операции – от элементарных логических соединений типа ИЛИ и И (OR, AND) до более сложных составных функций с инверсиями и приоритетами. В документации Microchip уделено внимание подробному описанию архитектуры одного BLE. Каждый элемент включает в себя 4-входовую LUT и триггер D для хранения состояния, что позволяет конфигурировать его как комбинаторный элемент или синхронный регистр. Важным моментом является то, что в пределах всего CLB существуют глобальные управляющие сигналы, такие как общий тактовый сигнал (CLBCLK), управляющие сигналы модуля включения и сброса (CLBMD/RESET/EN), а конкретные входы и конфигурация LUT задаются индивидуально для каждого BLE. Для представления и обработки конфигурации BLE удобно применить структурированный подход с использованием Python и dataclasses.

В рамках модели конфигурации BLE фиксируются 16-битная запись и выбранные варианты входных сигналов, которые обычно кодируются посредством 5-битных полей, указывающих источник входа для каждой линии LUT - A, B, C,D. Глубже погружаясь, полезно исследовать, какие именно входы доступны каждому из четырёх входов LUT. Согласно документации Microchip, для каждого входа возможен подключение к различным внутренним и внешним сигналам. Среди таких источников - сигналы других BLE, входные синхронизационные линии модуля CLB (CLB_IN_SYNC), а также сигналы счётчика, присутствующего в блоке. Этот широкий спектр входных вариантов позволяет создавать гибкие схемы с различным функционалом.

Для облегчения проектирования и конфигурирования логики на базе CLB Microchip предоставляет специализированный инструмент – CLB Synthesizer. Это веб-приложение и модуль для IDE MPLAB X, представляющий собой интерфейс с drag-and-drop функциональностью, позволяющий визуально создавать схемы и генерировать соответствующую конфигурацию. Программа использует Verilog описания и сопутствующие файлы ограничений (constraints), чтобы переводить разработку пользователя в конкретный битовый поток, управляющий настройками CLB. Рассматривая пример простейшего инвертора, составленного в CLB Synthesizer, можно увидеть, как исходный Verilog модулирует процесс работы, а файл ограниченийявляется связующим звеном между абстрактными именами цепей и физическими контактами микроконтроллера. При отправке этих файлов на backend-сервер синтеза получается детальная информация о скомпилированной логике в виде JSON-ответов и zip-архивов с внутренними файлами микрокода и визуализациями размещения логики.

Получение и анализ этих данных позволяют понять, как именно каждая LUT конфигурируется в аппаратном обеспечении, а также увидеть, как распределены BLE внутри CLB и как настраиваются входы и выходы. Особое значение приобретают расширенные файлы формата FASM (FPGA Assembly), отражающие низкоуровневое описание конфигураций перед преобразованием их в окончательный битовый поток, программируемый в устройство. Применение методики реверс-инжиниринга с последовательным изменением параметров LUT и изучением откликов в битовом потоке позволяет выявить точное соответствие битов конфигурации конкретным параметрам устройства. Вначале предполагалась возможность одновременной загрузки настроек для всех 32 BLE, однако практика показала, что синтезатор ограничен в масштабах заполнения и зачастую отказывается работать при попытке полной загрузки. Оптимальным подходом стало использование специальных входов CLBSWIN, разбитых на группы по восемь, чтобы направить входные сигналы соответствующим путём к LUT, таким образом минимизировать автоматическую оптимизацию синтезатора и сохранить структуру LUT неизменной.

Это позволило добиться стабильной работы при конфигурировании околодвадцати BLE. Дальнейшая работа заключалась в постепенном обходе и идентификации расположения каждого BLE на чипе через анализ сгенерированных маршрутов в SVG-файлах. Использование координатных обозначений (BLE_XxYy) помогло систематизировать его расположение и связать позицию с номером BLE. Это существенно упростило декодирование результатов синтеза и поддержку автоматизированного анализа позиционной информации. Интересным аспектом обратного анализа стало декодирование регистровых настроек входных мультиплексоров (MUX) CLB.

Понимание внутреннего распределения входных сигналов позволяло управлять ими по отдельности, создавая вариации в конфигурации и выявляя, какие биты битового потока отвечают за переключение источников сигналов и степень их синхронизации. Выявление битовых корреляций между изменениями входа и конфигурации позволило точнее определить структуру управляющих слов в битовом потоке. Также была пролита свет на параметры FLOPSEL - бит выбора режима триггера в BLE, позволяющий переключать базовые структуры от комбинационного логического узла к триггеру с синхронизацией на CLBCLK. Изучение и измерение корреляций с помощью программных скриптов дало представление о распределении этих битов на уровне микроконтроллера. Не оставался без внимания и встроенный счётчик в CLB, имеющий свои стоп и ресет входы.

Их взаимодействие с BLE и другими входами системы тщательно анализировалось для воссоздания полной картины модульных возможностей CLB. Анализ группировок и вариаций в битовом потоке помог составить модель этого функционала в виде Python dataclass. Конфигурация входных сигналов CLBIN и их союз с управляющими мультиплексорами была одной из ключевых задач. Возможность направлять одни и те же физические входы в разные каналы или с различной степенью синхронизации даёт дополнительные широты для реализации пользовательской логики. Разбор и понимание таких функций, как PPS (Peripheral Pin Select) – периферийный выбор выводов – и управляющих прерываний, позволил выявить их расположение и связь с конкретными битами в конфигурациях CLB.

Как оказалось, некоторые из этих настроек находятся вне непосредственного битового потока CLB, что выявило новые слои в архитектуре MCU. Детальный анализ также позволил составить карту битового распределения в рамках языкового описание CLKDIV – делителя частоты на триггерах, реализованного внутри CLB. Мануальное экспериментальное исследование дало результаты, которые сошлись с официальной документацией. В целом, проведение обратного анализа CLB Microchip принёс глубокое понимание внутреннего строения, способностей конфигурации и ограничений данного блока программируемой логики. Освоение таких техник позволит проектировщикам и энтузиастам точнее использовать возможности микроконтроллеров и создавать более надёжные, гибкие и эффективные решения с использованием CLB от Microchip.

Обратный инженеринг – это не только возможность улучшить документацию и инструментальные средства, но и открыть новые горизонты для творчества и инноваций в области встроенных систем.