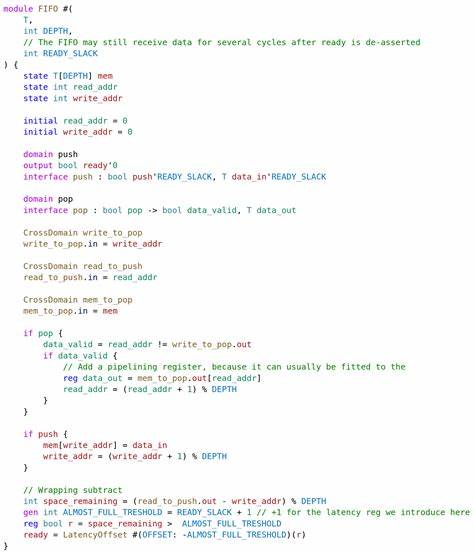

Разработка аппаратного обеспечения остаётся одной из ключевых областей, определяющих прогресс в цифровой электронике. Языки описания аппаратуры (HDL) играют главную роль в процессе создания схем и систем, позволяя инженерам моделировать, тестировать и внедрять сложные цифровые проекты. Среди традиционных языков Verilog и VHDL, которые на протяжении десятилетий были стандартом для описания аппаратных систем, появился SUS HDL — современный язык, призванный упростить и оптимизировать работу с синхронной логикой. SUS HDL выделяется своим подходом к управлению задержками и конвейеризацией. В отличие от классических решений, здесь компилятор автоматически отслеживает латентность и позволяет гораздо легче фиксировать временные характеристики системы.

Благодаря этому инженеры получают прозрачность и контроль над производительностью своих проектов, что особенно критично для высокопроизводительных аппаратных дизайнов, требующих тонкой настройки тайминга. Уникальная философия языка SUS заключается в минимализме синтаксиса и отказе от навязывания парадигм программирования. Это значит, что разработчик имеет максимальную свободу в представлении синхронной логики, не ограничиваясь шаблонами или конкретными протоколами взаимодействия. В итоге SUS предоставляет возможность отражать аппаратное устройство именно так, как оно задумано, не подвергая его дополнительным абстракциям, которые часто усложняют проектирование и отладку. Одним из заметных преимуществ SUS HDL становится мощное метапрограммирование.

Компилятор языка позволяет на этапе компиляции выполнять код, генерирующий lookup tables (LUT), что значительно облегчает создание повторяющихся структур и сложных вычислительных блоков. Такой подход экономит время и повышает качество проектирования, позволяя быстро создавать оптимизированные модули. В качестве примера можно рассмотреть реализацию деревообразного сумматора. В SUS HDL структура определяется рекурсивно с помощью генеративного кода, позволяя создавать модуль с параметризованной шириной, который эффективно складывает произвольное количество входных значений. Благодаря этому подходу код остаётся компактным, понятным и при этом легко масштабируется под разные аппаратные требования.

Особое внимание в SUS уделяется синхронности. Язык не поддерживает асинхронный дизайн, что ограничивает его применение в специализированных интегральных схемах, но обеспечивает сильную согласованность таймингов и предсказуемость поведения в цифровых системах, работающих на одном или нескольких тактовых генераторах. Это существенно облегчает разработку сложных цифровых устройств, таких как процессоры и области цифровой обработки сигналов, где отслеживание задержек особенно важно. Помимо технических преимуществ, SUS HDL уделяет большое внимание удобству работы и экспериментированию с аппаратными проектами. Редакторы и компиляторы обеспечивают визуальную поддержку и автоматическое отслеживание различных параметров, позволяя инженерам лучше понимать внутреннее устройство своих проектов без необходимости использования сторонних инструментов.

SUS HDL позиционируется как конкурент Verilog и VHDL не столько с точки зрения заменяемости, сколько как современный инструмент для проектировщиков, желающих работать более интуитивно и эффективно. Его открытая лицензия дает всем заинтересованным возможность участвовать в развитии проекта и адаптировать язык под свои нужды, что в свою очередь способствует созданию активного сообщества разработчиков и пользователей. Стоит отметить, что освоение языка не требует длительного времени. Имеется обучающее видео, охватывающее основные идеи и возможности SUS, позволяющее за менее чем час понять базовые принципы и начать писать собственные модули. Наличие активного сообщества и платформ для общения также поддерживает новых пользователей и способствует обмену опытом.

В итоге SUS HDL — это свежий взгляд на описание аппаратуры, соединяющий простоту и мощь современных языков программирования с особенностями цифровой логики. Его способности к автоматическому управлению задержками, эффективному метапрограммированию и полной прозрачности синхронных систем делают его привлекательным инструментом для инженеров и разработчиков, стремящихся создавать высокопроизводительные аппаратные решения с минимальными трудозатратами и максимальным контролем. Для тех, кто заинтересован в современном подходе к проектированию аппаратуры, SUS HDL предлагает эргономичную и гибкую платформу, которая способна легко встраиваться в существующие процессные цепочки и расширять возможности традиционных методов описания цифровых схем. В мире, где требования к производительности и надёжности цифровых систем постоянно растут, SUS HDL открывает новые горизонты для тех, кто хочет идти в ногу со временем в сфере аппаратного проектирования.