Современные вычислительные системы сталкиваются с беспрецедентным ростом требований к памяти, что связано с развитием технологий глубокого обучения, искусственного интеллекта и быстрого увеличения объёмов обрабатываемых данных. Одной из главных проблем является так называемая «стена памяти» — серьёзное ограничение, связанное с ограниченной пропускной способностью и ёмкостью памяти по сравнению с вычислительной мощностью процессоров. В этой ситуации эффективное статическое планирование памяти становится неотъемлемой частью обеспечения высокой производительности и экономного использования ресурсов. Статическое планирование памяти — это процесс оптимального размещения и назначения смещений для наборов буферов с известными размерами и временем жизни в адресном пространстве, цель которого — минимизация общего объёма используемой памяти. Несмотря на то что задача напоминает динамическое распределение памяти, она имеет уникальные особенности и ограничения, позволяющие применять специализированные алгоритмы оптимизации.

В основе проблемы лежит NP-полная комбинаторная задача, что означает трудности её решения классическими алгоритмами в приемлемое время при росте числа буферов. Традиционные подходы либо используют быстрые эвристики, зачастую приводящие к фрагментации и неэффективному использованию памяти, либо усиливают оптимизацию за счёт более сложных алгоритмов, но не способны масштабироваться на миллионы буферов — что становится критичным в рамках современных нейросетевых архитектур. Учёные из Национального технического университета Афин и KU Leuven представили инновационное решение — реализации алгоритма под кодовым названием idealloc. Этот подход направлен на низкофрагментированное, высокопроизводительное динамическое распределение памяти с возможностью обработки многомиллионных наборов буферов. Отличительной особенностью idealloc является применение продвинутых алгоритмических методик, основанных на результатах теории динамического планирования памяти и комбинированных стратегиях оптимизации.

В частности, рассматривается комплексный подход к назначению смещений буферов с учетом их размеров и периодов жизни, который позволяет максимально эффективно упаковать данные в минимальное адресное пространство. Такой подход крайне актуален в контексте глубокого обучения, где архитектуры нейросетей — статичны, а вычисления происходят на специализированных аппаратных ускорителях с физическим требованием непрерывного размещения данных в памяти. Помимо архитектурных факторов, важное значение имеет выбор оптимального алгоритма, способного обеспечить баланс между скоростью работы и минимизацией фрагментации. Методы, которые ранее были ограничены по масштабу из-за сложности вычислений, теперь благодаря idealloc демонстрируют высокую производительность и масштабируемость, позволяя обрабатывать большие наборы данных без значительных потерь в эффективности. В рамках исследований была осуществлена всесторонняя оценка на уникальной подборке сложных сценариев из разных доменов, что подтвердило превосходство idealloc по сравнению с четырьмя промышленными решениями.

Результаты показали высокую эффективность с точки зрения минимизации памяти и устойчивости алгоритма в разнообразных условиях. Данные достижения открывают новые перспективы для оптимизации программных и аппаратных платформ в областях, связанных с ресурсноёмкими вычислениями — таких как обработка больших данных, симуляторы, системы реального времени и, конечно, современные искусственные нейросети. Помня о сложности проблемы динамического распределения памяти, стоит заметить, что реализация idealloc почти преодолела «стену» масштабируемости, позволив перейти к статическому планированию памяти в системах размера миллионов буферов, что является значительным прорывом в индустрии. Таким образом, статическое планирование памяти сегодня — не просто эффективная оптимизация, но фундаментальный элемент будущих вычислительных платформ. Использование современных алгоритмов, таких как idealloc, улучшает не только производительность, но и снижает энергопотребление и стоимость аппаратных решений.

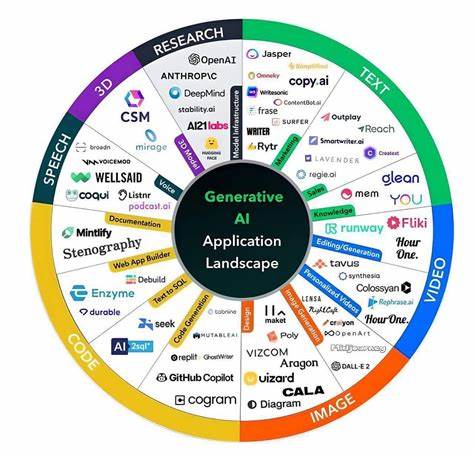

На фоне постоянного увеличения размеров и сложности нейросетевых моделей, а также возрастания требований к энергоэффективности, потребность в подобных инновациях будет только расти. Можно ожидать, что дальнейшие исследования и внедрение таких методик окажут значительное влияние на развитие индустрии в целом, способствуя созданию более мощных и оптимальных вычислительных систем. Важно отметить также междисциплинарный характер данной тематики, который объединяет компьютерную науку, алгоритмическую теорию, архитектуру процессоров и прикладную математику. Такой подход необходим для решения сложных проблем оптимизации, возникающих на стике теории и практики. В целом, будущие направления развития статического планирования памяти связаны с улучшением алгоритмической базы, внедрением машинного обучения для прогнозирования оптимальных стратегий размещения и расширением интеграции с аппаратным обеспечением, способным динамически адаптировать память под потребности приложений.

Эта эволюция позволит не только сохранить оперативность систем, но и значительно повысить их устойчивость к изменяющимся условиям эксплуатации. Таким образом, современное статическое планирование памяти — одна из ключевых задач будущего в области разработки вычислительных систем и искусственного интеллекта. Внедрение передовых технологий оптимизации памяти, таких как idealloc, является необходимым условием для преодоления существующих барьеров и создания эффективных платформ нового поколения.

![Futureproof Static Memory Planning [pdf]](/images/004F75E3-4EB2-4CC7-A49E-5DB7205BAD0C)